Introduction: In the intricate realm of ASIC design, precision isn't just a goal—it's the essence of excellence. The Universal Verification Methodology (UVM) and its Register Abstraction Layer (RAL) are pivotal, and this exploration delves into the strategic implementation of an automated SystemRDL parser in RAL. This approach, enriched by real-world UVM showcases, demonstrates the transformative power of precision and automation.

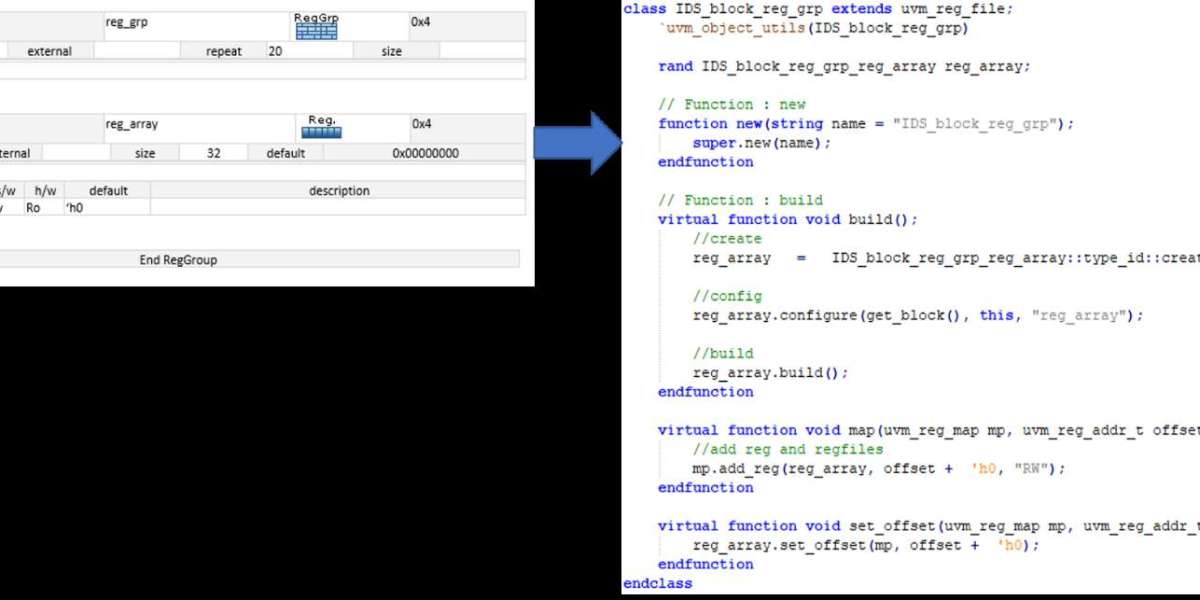

Unveiling the SystemRDL Parser in RAL: The SystemRDL parser emerges as a key player, navigating the path of precision in ASIC design. It brings a strategic edge to RAL implementation by offering a nuanced way to interpret and integrate register descriptions. This automated parsing not only simplifies the verification process but also introduces a layer of consistency crucial for the success of ASIC designs.

Automation as a Strategic Catalyst: Automation within the SystemRDL-driven RAL framework is a strategic catalyst. It liberates designers from manual efforts, reducing the risk of errors that could impede the verification process. This strategic approach extends to establishing uniformity across the design, aligning the verification environment seamlessly with the register specifications. In the complex landscape of ASIC designs, characterized by numerous registers demanding thorough validation, automation becomes the key to precision.

Elegance of SystemRDL Parsing: The SystemRDL parsing process unfolds with elegance, capturing register descriptions with precision. It involves interpreting registers, fields, and properties, ensuring a seamless integration process that enhances the collaboration between design and verification teams.

Harmony in Automation with Real-world UVM Showcases: Now, let's weave in the real-world UVM showcases to witness the tangible benefits of this precision-focused and automated approach. Imagine an ASIC design scenario with diverse IP blocks, each with distinct register specifications. UVM showcases offer a vivid demonstration of how the SystemRDL parser adapts to these diversities, showcasing precision, flexibility, and customization in action. These showcases provide concrete evidence of the dynamic nature of SystemRDL parsing in addressing real-world design complexities.

Strategic Solutions for Challenges: While automation is potent, addressing challenges strategically is imperative. Diverse register specifications across different IP blocks demand customization and flexibility in SystemRDL parsing tools. Robust error-handling mechanisms become vital to detect and rectify discrepancies, ensuring a seamless flow of precision from design to verification.

Conclusion: Navigating precision in ASIC design requires strategic tools, and the integration of an automated SystemRDL parser in the Register Abstraction Layer is a paradigm shift. Enriched by real-world UVM showcases, this precision-focused approach not only expedites the verification process but also elevates the overall quality of ASIC designs. As the semiconductor industry propels forward, embracing this strategically orchestrated automation, driven by SystemRDL parsing, becomes paramount for staying at the forefront of innovation and ensuring the resilience of ASIC products in an ever-evolving market.